AMD tampaknya yakin bahwa cache yang lebih besar membantu. Anda memiliki cache tak terbatas, Anda memiliki cache V dan dengan Zen 4 Anda juga harus mengembangkan cache L2. Genoa memiliki 1 megabyte per inti, dua kali lebih banyak dari Milan.

Menampilkan entri database di Geekbench Zen 4 dengan cache yang lebih besar. Tren di AMD jelas, karena mereka bekerja dengan cache yang lebih besar pada level yang berbeda. Prosesor mendapatkan V-Cache, kartu grafis mendapatkan Infinity Cache, dan Genoa harus mendapatkan dua kali cache L2 dengan satu MiB per inti. Setidaknya begitulah cara Geekbench membaca dari pola 100-000000479-13, yang memiliki 32 pusat. Tidak ada yang berubah di cache L3, yang masih 4 x 32MB, yaitu 128MB. Genoa juga diharapkan datang dengan cache 3D, yang menambahkan 64MB per chip. Pada akhirnya, AMD juga harus melihat apa yang dilakukan pesaing. Mereka juga menawarkan produk dengan cache besar. Sapphire Rapids dikatakan menawarkan 2 cache L2 MiB per inti dan secara opsional melengkapi cache L3 dengan memori HBM.

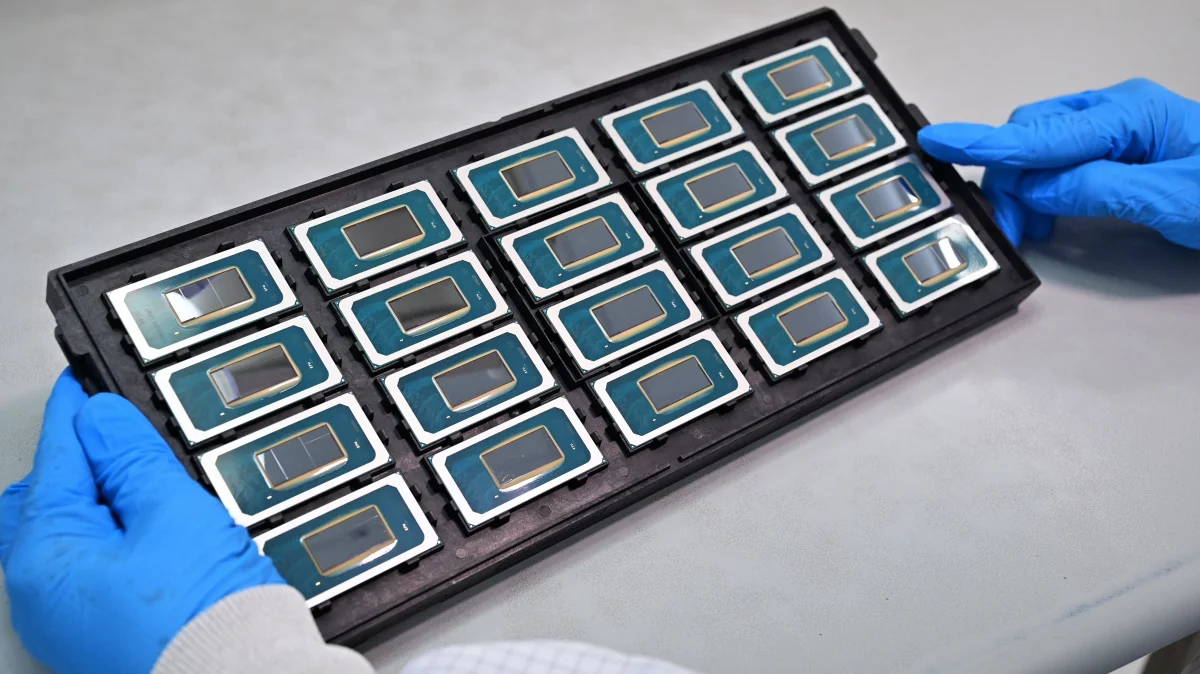

Prosesor tersebut dipasarkan dengan nama kode Genoa sebagai seri Epyc 7004; AMD telah mengumumkan ini. Seperti Bergamo (yang akan dimulai sedikit kemudian), Genoa didasarkan pada arsitektur Zen 4, yang diproduksi di TSMC pada 5 nanometer. Prosesor Genoa dilengkapi dengan hingga 96 inti, yang disusun ke dalam hingga 12 pengontrol pengisian daya per paket. DDR5 didukung pada 5200Mbps pada 12 saluran dan 12TB harus diinstal jika 512 kaset digunakan – tetapi dalam konfigurasi penuh kemungkinan hanya dengan 4000Mbps. Sementara itu, tersedia PCI Express 5.0 dengan 128 jalur. TDP akan mencapai puncaknya sekitar 400 watt. Lebih jelasnya, seperti tarif per jam, tentu belum diketahui. Sampel yang disebutkan berasal dari laporan Geekbench dengan 1.2GHz, yang menunjukkan sampel teknik.

Bergamo dikatakan sebagai pengembangan lebih lanjut dari Genoa, yang menawarkan 128 core. Sangat mungkin bahwa AMD akan menggandakan core dengan prosesor yang kuat dan mengambil langkah pertama menuju desain hybrid penuh dengan Zen 5, seperti yang telah dibahas dalam rumor desktop Zen 4 (Raphael). Masalah lainnya adalah SMT menjatuhkan Bergamo agar tetap berada di jendela TDP di satu sisi dan mengurangi risiko keamanan di sisi lain, karena SMT adalah vektor serangan untuk serangan saluran samping. Cache 3D yang diperkenalkan, yang ditumpuk di bagian belakang dalam bentuk L3, harus mampu hingga 768MB. Berkat desain MCM, AMD dapat mengonfigurasi konfigurasi semua CPU sepenuhnya satu per satu.

Sumber: melalui Twitter (penyematan tweet)

“Coffee pioneer. Social media ninja. Unrepentant web teacher. Friendly music fan. Alcohol fanatic.”

More Stories

Intel dilaporkan ingin menghadapi Strix Halo AMD dengan GPU raksasanya sendiri di prosesornya

Ponsel Pixel 8 Pro dengan tarif 5G + jam tangan pintar gratis

Ponsel cerdas Pixel dikirimkan melalui pemeliharaan jarak jauh yang dilakukan secara diam-diam namun tidak aktif